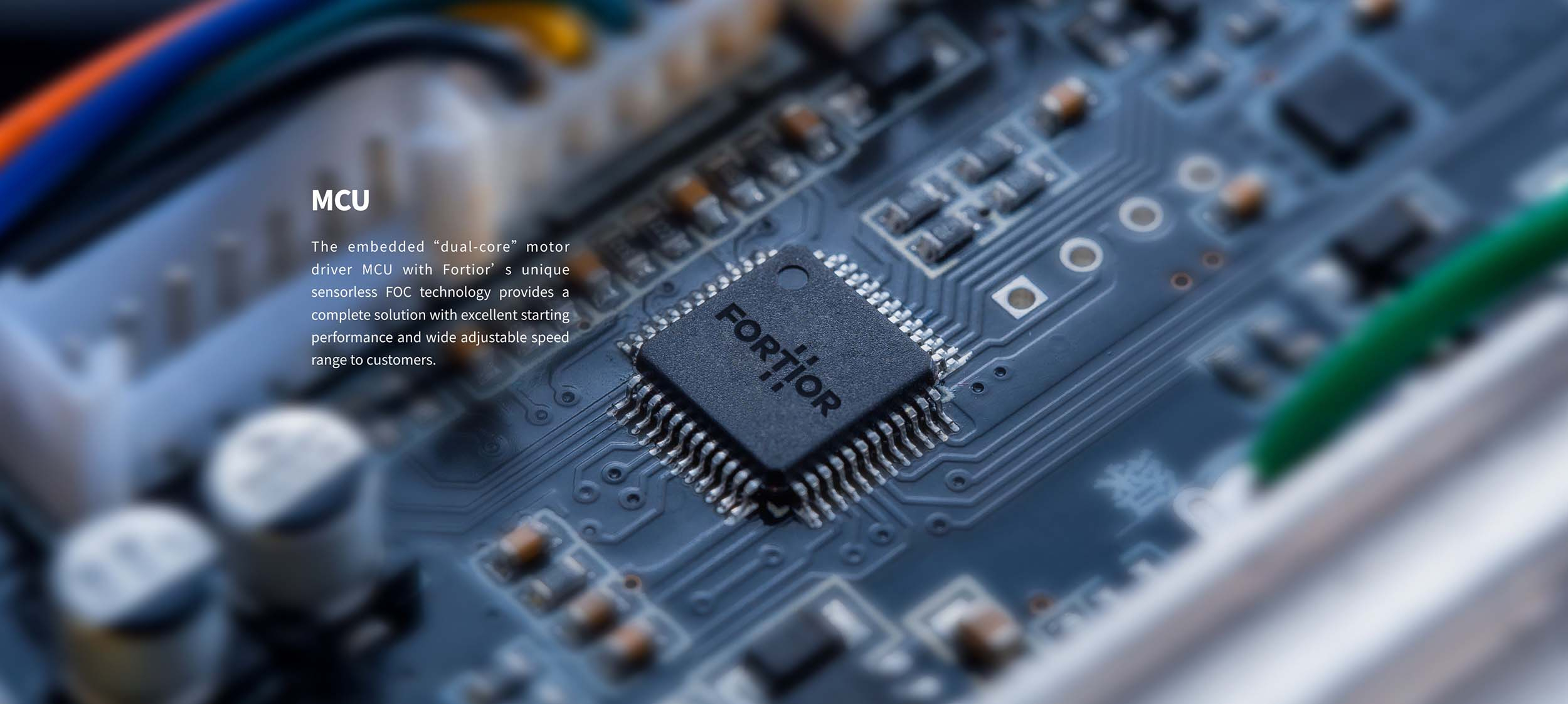

EU6361Q

- Description

- The high-performance motor drive chip incorporates ME core and 8051 core. ME core implements

motor control in real time and 8051 core is used for parameter configuration and routine processing. The dual

cores work in parallel to achieve high-performance motor control. The chip integrates high-speed operational

amplifiers, comparators, high-speed ADC, multiplier/divider, CRC, SPI, I2C, UART, Timers, PWM modules,

built-in high-voltage LDO, which are suitable for FOC or square-wave based BLDC/PMSM motors.

Package type of the chip: QFN56

- Features

-

◼ Power supply:

➢ Single-power supply mode: When VCC_MODE = 0, external power supply 5V~24V is connected

to VCC pin, and internal LDO supplies VDD5 voltage.

➢ Dual-power supply mode: When VCC_MODE = 1, external power supply 1 (5V~36V) is

connected to VCC pin, and external power supply 2 (5V) is connected to VDD5 pin. VCC≥VDD5.

◼ Dual core: 8051 core and ME core

◼ An instruction cycle mostly takes 1 or 2 system clock cycle(s)

◼ 16kB Flash ROM with CRC, self-program and code protection

◼ 256 bytes IRAM and 768 bytes XRAM

◼ ME: Core integrating LPF module, PI regulator, BLDC module, FOC module, MDU auxiliary

computing module

◼ 1T 16x16 multiplier, 16T 32/16 divider

◼ 16 interrupt sources with 4 configurable priority levels

◼ 30*GPIOs

◼ Timers:

➢ 2*Programmable timers with capture feature

➢ 1*QEP decoding programmable timer

➢ 1*BLDC motor dedicated timer

➢ 1*General-purpose timer

➢ 1*RTC

◼ Communication interfaces:

➢ 1*SPI

➢ 1*I2C

➢ 2*UARTs, supporting single-wire mode

➢ Dual-channel DMA: supporting data transmission via I2C/SPI/UART

◼ Analog Peripherals:

➢ 12-bit ADC, operating with 1μs conversion time and internal VREF or external VREF

selectable as reference voltage

➢ Number of ADC channels: 12

➢ Internal VREF. 3V, 4V, 4.5V and VDD5 can be selected as the internal reference.

➢ Internal VHALF, with 1/2 VREF as the internal reference

➢ Three standalone operational amplifiers

➢ 3-channel analog comparator

➢ Single-channel 9-bit DAC (DAC0)

◼ Driver Type:

➢ 6N Pre-driver

◼ FOC module supports single/dual/triple-shunt current sampling

◼ FOC module supports overmodulation

◼ Automatic commutation, cycle-by-cycle current limiting and Hall/BEMF-based position sensing

for BLDC motor control

◼ System clock

➢ Built-in 24MHz high-speed oscillator

➢ Built-in 32.8kHz low-speed oscillator

◼ WDT

◼ LVD

◼ TSD

◼ Two-wire FICE protocol based in-circuit emulation

◼ Magnetoresistance (MR) angle sensor

- Package

-

QFN56

- Datasheet

-

Download